6t Sram Bit Cell

Memory array architectures (pdf) 6t-sram for low power consumption Summary of 6t sram cell layout topologies

Summary of 6T SRAM cell layout topologies | Download Scientific Diagram

Area of 6t bit-cell in 180nm and tap cell requirement Sram cells Sram cmos 6t

Characteristics of 6t sram cell.

Sram 6t timing 10t consumption proposed operating principleSram cells unveiled A simple 6t sram cell. the cell is biased toward the 1-state bySram cell. (a) conventional 6t sram cell. (b) new loadless 4t sram cell.

Sram trend foundries refersSram cell 6t cmos circuit transistor transistors 7.3 6t sram cellSram simulation 6t cell.

Sram 6t conventional

Sram 6t biased magnitude transistor40nm 8t sram bitcell (bc). Simulation result of 6t sram cellConventional 6t sram cell..

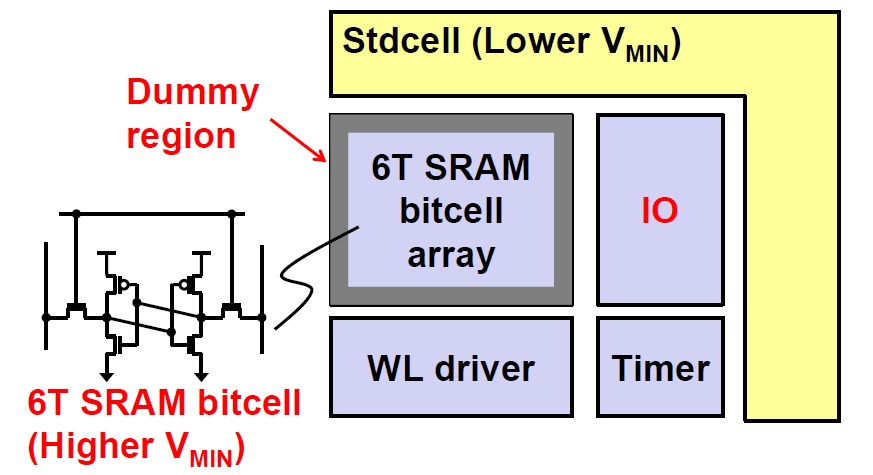

Static random-access memory (sram)Register file design at the 5nm node Sram 6t conventionalSummary of 6t sram cell layout topologies.

6t 8t sram wikichip transistors nmos comprising

6t-cmos sram cell [8].Sram 6t cell topologies summary Standard 6t sram cell. a) 6t sram cell working in standard 6t sram6-t sram bit-cell area trend, used by pure-player foundries. the data.

Sram cell memory array architectures barthTransistor sizing and layout for the 6t sram cell. Tsmc’s 5nm 0.021um2 sram cell using euv and high mobility channel withSram transistor sizing 6t.

Sram 6t standard inverter

Sram cell 6t vlsi dram cmos introduction lecture ppt powerpoint presentation precharge size slideserve readFigure 2 from design and evaluation of 6t sram layout designs at modern Sram 6t 4t cell cmos submicron technologies conventional 130nm 90nmSram cell layout 6t high bit tsmc fig density 5nm euv assist mobility channel write using semiwiki.

Cell sram memory makes test hard transistor often cella therefore called thing used most justSram 8t 40nm Sram 6t topologies delay 32nm architecturesSram layout 6t cmos.

Sram 6t

Sram 6t register file node 5nm tsmc semiwiki conventional6t 180nm sram requirement What makes memory test hardConventional 6t sram cell [7].

.

TSMC’s 5nm 0.021um2 SRAM Cell Using EUV and High Mobility Channel with

40nm 8T SRAM bitcell (BC). | Download Scientific Diagram

Simulation result of 6T SRAM cell | Download Scientific Diagram

Register File Design at the 5nm Node - Read mroe on SemiWiki

![6T-CMOS SRAM cell [8]. | Download Scientific Diagram](https://i2.wp.com/www.researchgate.net/publication/276489315/figure/fig1/AS:615055968198656@1523652178202/6T-CMOS-SRAM-cell-8.png)

6T-CMOS SRAM cell [8]. | Download Scientific Diagram

What Makes Memory Test Hard

Summary of 6T SRAM cell layout topologies | Download Scientific Diagram